NovalMS, V.2.0 V.Lobo 2021

NovalMS, V.2.0 V.Lobo 2021

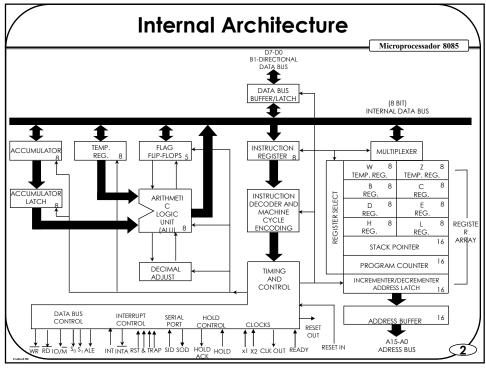

REGISTERS Microprocessador 8085 General use registers - There is 1 privileged register, named ACCUMULATOR, that is always used to store:  $\rightarrow$ one of the arguments of arithmetic and logic operations  $\rightarrow$ The result of arithmetic and logic operations - There are 6 general use 8 bit registers, that are sometimes used in pairs to "form 16 bit registers" One the register pairs (H and L, or High & Low) are used to generate addresses. The datum contained in the memory position whose address is stores in HL is sometimes treated as if if ware a register (Register M), and is refered to as M or [HL] FFFF Α 64k B С (65536 . memory Ε M D , addresses) н 0000 Main memory 4 4

NovalMS, V.2.0 V.Lobo 2021

NovalMS, V.2.0 V.Lobo 2021

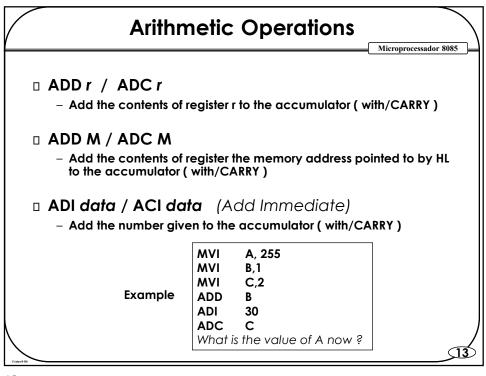

13

NovalMS, V.2.0 V.Lobo 2021

NovalMS, V.2.0 V.Lobo 2021

NovalMS, V.2.0 V.Lobo 2021

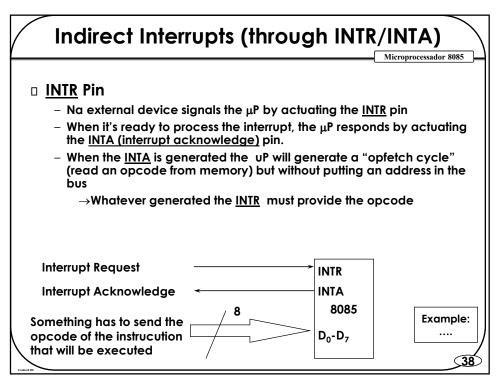

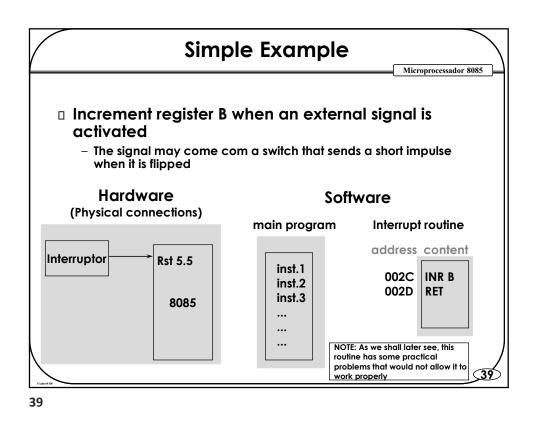

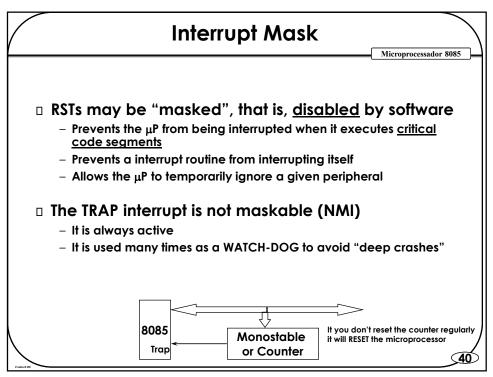

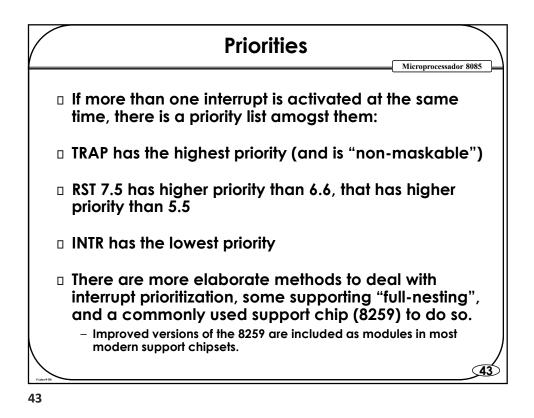

| $\square$ |                                                                                                                                                                                                                                                                          | interrupts | icroprocessador 8085      |     |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|-----|--|--|--|--|--|--|--|

|           | <ul> <li>IRAP and RST pins         <ul> <li>When these pins are actuated, they force the μP to execute a RST instruction</li> <li>A CALL insctruction is executed to a given address : addr = (number of the Rst) x 8</li> <li>There 4 such pins:</li> </ul> </li> </ul> |            |                           |     |  |  |  |  |  |  |  |

|           | Pin                                                                                                                                                                                                                                                                      | Address    | Type of actuation         | on  |  |  |  |  |  |  |  |

|           | RST 5.5                                                                                                                                                                                                                                                                  | 2CH        | by level ("1")            |     |  |  |  |  |  |  |  |

|           | RST 6.5                                                                                                                                                                                                                                                                  | 34H        | by level ("1")            |     |  |  |  |  |  |  |  |

|           | RST 7.5                                                                                                                                                                                                                                                                  | 3CH        | by flank (0->1) (it has a | FF) |  |  |  |  |  |  |  |

|           | TRAP (RST 4.5)                                                                                                                                                                                                                                                           | 24 H       | by maintaining a "1'      |     |  |  |  |  |  |  |  |

NovalMS, V.2.0 V.Lobo 2021

NovalMS, V.2.0 V.Lobo 2021

| Hardware and e                                                                          | external connections                              |                                                                         |                          |                      |               |                                 |

|-----------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|--------------------------|----------------------|---------------|---------------------------------|

| There are many                                                                          | X1<br>X2<br>Reset Out                             | + + ↓                                                                   | 1<br>2<br>3              |                      | <b>t</b> † †  | Vcc (+5V)<br>Hold<br>Hlda       |

| different<br>"packaging"options"                                                        | SOD<br>SID<br>TRAP<br>RST 7.5                     | $\downarrow \uparrow \uparrow \uparrow$                                 | 6                        | 36<br>35             |               |                                 |

| <ul> <li>The most common is<br/>DIP-40 (Dual In-line<br/>Packaging) with TTL</li> </ul> | RST 6.5<br>RST 5.5<br>INTR<br>~INTA<br>AD0<br>AD1 | $\uparrow$ $\uparrow$ $\uparrow$ $\downarrow$ $\downarrow$ $\downarrow$ | 8<br>9<br>10<br>11<br>12 | 33<br>32<br>31<br>30 | <u> </u>      | S1<br>~RD                       |

| <ul><li>levels</li><li>Pinout of the 8085 in</li></ul>                                  | AD1<br>AD2<br>AD3<br>AD4<br>AD5                   | $\leftrightarrow$                                                       |                          | 27<br>26<br>25       | $\rightarrow$ | A15<br>A14<br>A13<br>A12<br>A11 |

| DIP-40:                                                                                 | AD6<br>AD7<br>Vss                                 | ¢ ¢ ↑                                                                   | 19                       | 23<br>22<br>21       | 1.            | A19<br>A9<br>A8                 |

|                                                                                         |                                                   |                                                                         |                          |                      | -             | 4                               |

NovalMS, V.2.0 V.Lobo 2021

Página 27

NovalMS, V.2.0 V.Lobo 2021

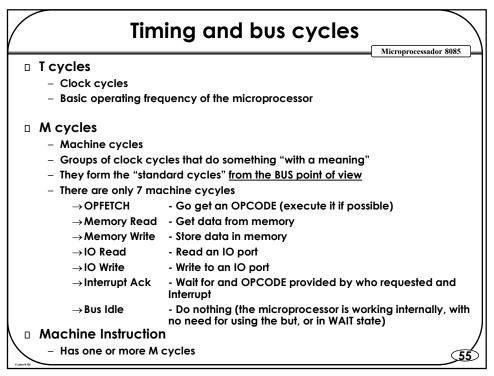

55

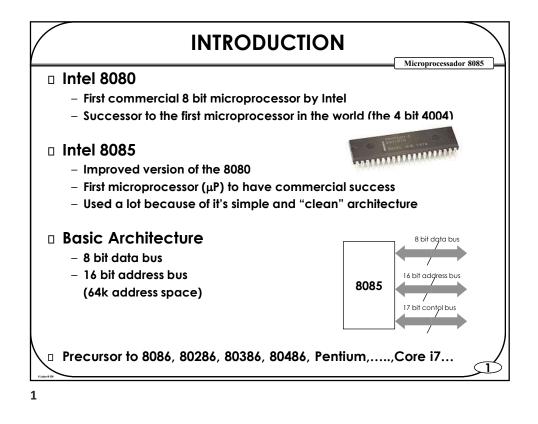

# 8085 Microprocessor NovalMS, V.2.0 V.Lobo 2021